### **Zmluva**

# o poskytnutí finančných prostriedkov na spolufinancovanie projektu výskumu a vývoja ENIAC č. 324280/2012

Časť projektu: "Multipulzné testovanie spoľahlivosti výkonových prvkov pomocou UIS testovania pri vysokých teplotách"

Poskytovateľ: Ministerstvo školstva, vedy, výskumu a športu SR

sídlo: Stromová 1, 813 30, Bratislava

zastúpený štatutárnym.

orgánom: doc. PhDr. Dušanom Čaplovičom, DrSc.

ministrom

osoba oprávnená rokovať

v odborných veciach: Ing. Róbert Szabó, PhD., GR SVT

Tel. číslo: 02/59374711 Fax: 02/59374722

e-mail: robert.szabo@minedu.sk

Ing. Marta Fábiková, odbor IŠPVV

Tel. číslo: 02/59374734

e-mail: marta.fabikova@minedu.sk

IČO: 00 164 381

Bank. spojenie: Štátna pokladnica, č. účtu 7000065236/8180

(d'alej len "poskytovatel"")

Príjemca: NanoDesign, s.r.o.

sídlo: Drotárska 6385/19a, 811 04, Bratislava

zastúpený štatutárnym

orgánom: Ing. Martin Daříček, PhD.

osoba oprávnená rokovať

v odborných veciach: Ing. Martin Daříček, PhD. Tel. číslo: +421 903 968 243

Fax:

e-mail: martin.donoval@nanodesign.sk

IČO:

36744930

DIČ:

2022343873

peňažný ústav:

Tatra banka a.s.

číslo účtu:

2921884831 /1100

Zapísaný: V obchodnom registri Okresného súdu Bratislava I, vložka č.

44813/B

(d'alej len "príjemca")

### Preambula

Nariadením Rady (ES) č. 72/2008 z 20. decembra 2007 bol založený spoločný európsky technologický podnik ENIAC (ďalej len "spoločný podnik") na podporu spoločných európskych výskumných a vývojových aktivít v oblasti nanoelektroniky. Slovenská republika sa prihlásila za člena spoločného podniku listom podpredsedu vlády a ministra školstva SR zo dňa 12. decembra 2008 a zaviazala sa alokovať každoročne v rozpočtovej kapitole Ministerstva školstva Slovenskej republiky prostriedky štátneho rozpočtu Slovenskej republiky vo výške 500 000 eur za účelom spolufinancovania účasti organizácií výskumu a vývoja v Slovenskej republike v projektoch výskumu a vývoja spoločného podniku (ďalej len "projekt spoločného podniku").

Na základe dohody o administrácii č. ENIAC-ED-27-09 uzavretej medzi spoločným podnikom a Ministerstvom školstva SR, ktorá je neoddeliteľnou súčasťou tejto zmluvy v Prílohe 1, sa Ministerstvo školstva SR stalo národným financujúcim orgánom, ktorý zabezpečuje poskytovanie prostriedkov štátneho rozpočtu Slovenskej republiky na spolufinancovanie účasti organizácií výskumu a vývoja v Slovenskej republike v projektoch spoločného podniku.

# Čl. 1 Predmet zmluvy

- 1) Poskytovateľ a príjemca uzatvárajú túto zmluvu podľa Čl. 13 ods. 6 písm. b) Štatútu spoločného podniku ENIAC, ktorý je neoddeliteľnou súčasťou Nariadenia Rady (ES) č. 72/2008 z 20. decembra 2007, ktorým sa zakladá spoločný podnik ENIAC (ďalej len "štatút spoločného podniku").

- 2) Poskytovateľ a príjemca sa dohodli na predmete zmluvy na základe technickej špecifikácie Technical Anex E2COGaN Energy Efficient Converters using GaN Power Devices (ďalej len "technická špecifikácia), ktorá bola schválená spoločným podnikom dňa 9. januára 2013 a je v Prílohe 2 k tejto zmluve, ktorá je jej neoddeliteľ nou súčasť ou.

- 3) Predmetom zmluvy je poskytnutie 94 500 EUR (slovom deväťdesiatštyritisíc päťsto EUR) z prostriedkov štátneho rozpočtu Slovenskej republiky poskytovateľom príjemcovi na zabezpečenie spolufinancovania riešenia projektu spoločného podniku s názvom "Energeticky efektívne konvertory na báze GaN výkonových súčiastok (E2COGaN)", ktorého riešenie bolo schválené na základe výberového konania uskutočneného spoločným podnikom k výzve ENIAC Call 2012-1 pre verejnú súťaž ním vyhlásenej v roku 2012 a potvrdené "technickou špecifikáciou".

- 4) Doba riešenia projektu spoločného podniku je stanovená v "technickej špecifikácií" schválenej spoločným podnikom.

- 5) Poskytovateľ zabezpečuje spolufinancovanie riešenia projektu spoločného podniku počas celej doby jeho riešenia, ktorá je 36 mesiacov.

- 6) Príjemca sa zaväzuje zabezpečiť riešenie projektu č. 324280/2012 s názvom: "Energeticky efektívne konvertory na báze GaN výkonových súčiastok", ("E2COGaN Energy Efficient Converters using GaN Power Devices"), časť projektu: "Multipulzné testovanie spoľahlivosti výkonových prvkov pomocou UIS testovania pri vysokých teplotách" počas celej doby jeho riešenia od: 01/04/2013 do: 31/03/2016.

7) Špecifikácia projektu spoločného podniku (zoznam riešiteľov a ich kapacít viazaných na riešenie projektu, použitia prostriedkov štátneho rozpočtu Slovenskej republiky poskytnutých poskytovateľom vrátane charakteristiky, cieľov projektu v jednotlivých rokoch jeho riešenia a výstupov) je uvedená v Prílohe 3, ktorá je neoddeliteľnou súčasťou zmluvy.

# Čl. 2 Poskytovanie a použitie prostriedkov

- 1) Financovanie projektu spoločného podniku sa uskutočňuje podľa Čl. 13 štatútu spoločného podniku.

- 2) Spoločný podnik podľa Čl. 13 ods. 6 písm. a) štatútu spoločného podniku poskytuje príjemcovi na spolufinancovanie riešenia projektu spoločného podniku prostriedky zo svojho rozpočtu vo výške 15,0 % z celkových oprávnených nákladov na riešenie projektu spoločného podniku.

- 3) Poskytovateľ poskytuje príjemcovi, ktorý je podnikateľom podľa zákona č. 513/1991 Zb. (Obchodný zákonník) v znení neskorších predpisov na spolufinancovanie riešenia projektu spoločného podniku prostriedky štátneho rozpočtu Slovenskej republiky vo výške 35,0 % z celkových oprávnených nákladov na riešenie projektu spoločného podniku.

- 4) Oprávnenými nákladmi na riešenie projektu spoločného podniku, ktoré financuje poskytovateľ z prostriedkov štátneho rozpočtu Slovenskej republiky, sú náklady podľa § 17 ods. 2 až 5 zákona č. 172/2005 Z. z. o organizácii štátnej podpory výskumu a vývoja a o doplnení zákona č. 575/2001 Z. z. o organizácii činnosti vlády a organizácii ústrednej štátnej správy v znení neskorších predpisov v znení neskorších predpisov a rozpočet projektu spoločného podniku hradený z prostriedkov štátneho rozpočtu Slovenskej republiky je špecifikovaný príjemcom v časti C. Prílohy 3 k tejto zmluve.

- 5) Príjemca si za účelom poskytnutia prostriedkov štátneho rozpočtu Slovenskej republiky poskytovateľom a ich transparentného čerpania zriadi osobitný účet (ďalej len "účet príjemcu").

- 6) Poskytovateľ poskytuje prostriedky štátneho rozpočtu Slovenskej republiky na účet príjemcu v jednotlivých rokoch riešenia projektu spoločného podniku podľa rozpisu celkových oprávnených nákladov uvedených v Prílohe 4 k tejto zmluve, ktorá je jej neoddeliteľ nou súčasťou.

- 7) V prvom rozpočtovom roku riešenia projektu poskytovateľ poskytne prostriedky štátneho rozpočtu Slovenskej republiky na účet príjemcu v lehote do 20 pracovných dní odo dňa účinnosti tejto zmluvy.

- 8) V ďalších rokoch riešenia projektu spoločného podniku poskytovateľ poskytuje prostriedky štátneho rozpočtu Slovenskej republiky na účet príjemcu na základe výsledkov monitorovania a technického auditu projektu spoločného podniku, ktoré vykonáva spoločný podnik a na základe kontroly použitia prostriedkov štátneho rozpočtu Slovenskej republiky poskytnutých príjemcovi v predchádzajúcom rozpočtovom roku, ktorú vykonáva poskytovateľ.

- 9) Poskytovateľ poskytuje prostriedky štátneho rozpočtu Slovenskej republiky v ďalších rokoch riešenia projektu spoločného podniku na účet príjemcu na základe dodatkov k tejto zmluve.

- 10) Ak v prvom rozpočtovom roku riešenia projektu spoločného podniku sú prostriedky štátneho rozpočtu Slovenskej republiky poskytnuté poskytovateľom omeškane na účet príjemcu voči termínu začatia riešenia projektu spoločného podniku, ktorý je záväzne stanovený spoločným podnikom v "technickej špecifikácii", z dôvodu omeškania podpísania zmluvy medzi príjemcom a poskytovateľom alebo medzi príjemcom a spoločným podnikom, môže príjemca na financovanie projektu spoločného podniku použiť vlastné prostriedky, ktoré si potom refunduje z prostriedkov vedených na účte príjemcu.

- 11) Rovnako v ďalších rokoch riešenia projektu spoločného podniku, ak poskytovateľ poskytne prostriedky štátneho rozpočtu Slovenskej republiky na účet príjemcu omeškane, môže príjemca počas meškania použiť na riešenie projektu spoločného podniku vlastné prostriedky, ktoré si potom refunduje z prostriedkov vedených na účte príjemcu.

- 12) Príjemca môže prostriedky štátneho rozpočtu Slovenskej republiky poskytnuté poskytovateľom na účet príjemcu použiť iba na stanovený účel.

- 13) Bežné výdavky, ktoré boli poskytnuté príjemcovi po 1. októbri rozpočtového roka, a ktoré nebolo možné použiť do konca príslušného rozpočtového roka možno použiť do 31. marca nasledujúceho rozpočtového roka v súlade s § 8 ods. 5 zákona č. 523/2004 Z. z. o rozpočtových pravidlách verejnej správy a o zmene a doplnení niektorých zákonov.

- 14) Použitie finančnej dotácie podlieha povinnému ročnému zúčtovaniu so štátnym rozpočtom v zmysle § 8a ods. 7 zákona č. 523/2004 Z. z. o rozpočtových pravidlách verejnej správy a o zmene a doplnení niektorých zákonov najneskôr v termíne a spôsobom určenom Ministerstvom financií SR na zúčtovanie finančných prostriedkov štátneho rozpočtu. Zúčtovanie finančnej dotácie poskytnutej prijímateľovi v nasledujúcich kalendárnych rokoch v zmysle dodatkov k tejto zmluve bude vykonané v zmysle podmienok stanovených Ministerstvom financií SR k zúčtovaniu finančných vzťahov so štátnym rozpočtom na daný kalendárny rok.

- 15) Prostriedky vyplývajúce zo zúčtovania je príjemca povinný bez zbytočného odkladu vrátiť po 31. 3. 2013 na depozitný účet poskytovateľa 7000063900/8180, Štátna pokladnica, variabilný symbol číslo 11. O vratke nepoužitých prostriedkov je príjemca povinný poslať písomné oznámenie odboru učtárne a styku so Štátnou pokladnicou poskytovateľa.

- 16) Príjemca zodpovedá za hospodárenie s prostriedkami štátneho rozpočtu Slovenskej republiky poskytnutými poskytovateľom na účet príjemcu a je povinný pri ich použití zachovávať hospodárnosť, efektívnosť a účelnosť ich použitia.

- 17) Výnos, ktorý vznikol z účtu príjemcu, je podľa § 7 ods. 1 písm. m) zákona č. 523/2004 Z. z. o rozpočtových pravidlách verejnej správy a o zmene a doplnení niektorých zákonov v znení neskorších predpisov v spojení s Metodickým usmernením Ministerstva financií Slovenskej republiky číslo MF/7415/2005-421 príjmom štátneho rozpočtu Slovenskej republiky.

- 18) Výnosom určeným na vykonanie odvodu, sú prostriedky, ktoré zostali na účte príjemcu po odpočítaní celého poplatku za vedenie účtu príjemcu od úrokov pripisovaných bankou.

- 19) Lehota na vykonanie odvodu výnosov z prostriedkov štátneho rozpočtu Slovenskej republiky vedených na účte príjemcu na účet poskytovateľa č. 7000063812/8180 je do 31.3. nasledujúceho rozpočtového roka.

- 20) Ak riešenie projektu spoločného podniku vyžaduje zaobstaranie tovarov, služieb a prác, príjemca je povinný v cene pre ich zaobstaranie zohľadniť najlepší pomer kvality a výšky ceny.

- 21) Príjemca pri zaobstarávaní tovarov, služieb a prác z prostriedkov štátneho rozpočtu Slovenskej republiky vedených na účte príjemcu musí postupovať podľa zákona č. 25/2006 Z. z. o verejnom obstarávaní a o zmene a doplnení niektorých zákonov v znení neskorších predpisov.

# Čl. 3 Práva a povinnosti

- 1) Príjemca a poskytovateľ zodpovedajú za včasné a riadne plnenie si povinností podľa tejto zmluvy.

- 2) Príjemca je povinný všetky náklady súvisiace s riešením projektu doložiť prehľadom o výške, spôsobe a účele čerpania finančných prostriedkov, vypracovaných podľa skutočných nákladov na riešenie projektu a platných usmernení a pokynov poskytovateľa v termíne do 31. januára nasledujúceho rozpočtového roka.

- 3) Príjemca je povinný uchovávať všetky dokumenty a doklady, vrátane účtovných dokladov, týkajúcich sa projektu spoločného podniku najmenej počas piatich rokov nasledujúcich po roku, kedy skončí doba spolufinancovania projektu spoločného podniku poskytovateľom.

# Čl. 4 Kontrola

- 1) Monitorovanie a kontrolu riešenia projektu spoločného podniku vykonáva spoločný podnik podľa Čl. 7 ods. 3 písm. j) a k) štatútu spoločného podniku.

- 2) Poskytovateľ akceptuje závery vyplývajúce z monitorovacích správ a výsledkov kontroly riešenia projektu spoločného podniku vykonaných spoločným podnikom.

- 3) Poskytovateľ je oprávnený vykonať pre svoje potreby finančnú kontrolu podľa zákona č. 502/2001 Z. z. o finančnej kontrole a vnútornom audite a o zmene a doplnení niektorých zákonov v znení neskorších predpisov počas trvania zmluvného vzťahu medzi ním a príjemcom ako aj po jeho ukončení, a to aj v prípade odstúpenia od zmluvy.

4) Príjemca je povinný pri výkone kontroly alebo auditu dodržiavať ustanovenia § 14 ods. 2 a § 35 ods. 8 zákona č. 502/2001 Z. z. o finančnej kontrole a vnútornom audite a o zmene a doplnení niektorých zákonov v znení neskorších predpisov.

# Čl. 5 Odstúpenie od zmluvy

- 1) Poskytovateľ má právo odstúpiť od zmluvy, ak

- a) si príjemca neplní povinnosti stanovené v tejto zmluve,

- riešenie projektu spoločného podniku má závažné chyby, ktoré zistil spoločný podnik pri monitorovaní a kontrole riešenia projektu spoločného podniku, alebo také chyby, že čas na ich odstránenie by do značnej miery znehodnotil cieľ riešenia projektu spoločného podniku,

- c) spoločný podnik odstúpi od zmluvy medzi ním a príjemcom z ďalších dôvodov stanovených v zmluve medzi ním a príjemcom,

- d) dôjde k zrušeniu spoločného podniku.

- 2) Ak poskytovateľ odstúpi od zmluvy medzi ním a príjemcom z dôvodov podľa Čl. 5 ods. 1 písm. a) až c) tejto zmluvy, má právo požadovať vrátenie všetkých prostriedkov štátneho rozpočtu Slovenskej republiky ním poskytnutých príjemcovi.

- 3) Ak poskytovateľ odstúpi od zmluvy medzi ním a príjemcom z dôvodov podľa Čl. 5 ods. 1 písm. d), má právo požadovať vrátenie časti prostriedkov štátneho rozpočtu Slovenskej republiky, ktoré boli použité príjemcom po termíne zrušenia spoločného podniku.

- 4) Príjemca pri naplnení ods. 2 Čl. 5 a ods. 3 Čl. 5 zmluvy poskytnuté prostriedky vráti bez zbytočného odkladu a to:

- na výdavkový účet poskytovateľa č. 7000065236/8180, ak sa prostriedky vracajú v tom istom rozpočtovom roku, v ktorom boli poskytnuté príjemcovi,

- na príjmový účet poskytovateľa č. 7000063820/8180, ak sa prostriedky vracajú v inom rozpočtovom roku, v ktorom boli poskytnuté príjemcovi.

- 5) Príjemca má právo odstúpiť od zmluvy v prípade, ak si poskytovateľ neplní povinnosti stanovené v tejto zmluve.

- 6) Príjemca je povinný prostriedky štátneho rozpočtu Slovenskej republiky neoprávnene použité na iný účel než účel stanovený v predmete zmluvy vrátiť na príjmový účet poskytovateľa.

## Čl. 6 Sankcie

Sankcie za porušenie finančnej disciplíny príjemcom pri hospodárení s prostriedkami štátneho rozpočtu Slovenskej republiky sa riadia § 31 zákona č. 523/2004 Z. z. o rozpočtových pravidlách verejnej správy a o zmene a doplnení niektorých zákonov v znení neskorších predpisov.

## Čl. 7 Vlastnícke práva k predmetu zmluvy

Vlastnícke práva k výsledkom riešenia projektu spoločného podniku sa riadia podľa ustanovení Čl. 23 štatútu spoločného podniku.

### Čl. 8 Záverečné ustanovenia

- 1) Príjemca a poskytovateľ sa zaväzujú bezodkladne navzájom sa písomne informovať o zmenách identifikačných údajov uvedených v zmluve a akýchkoľvek iných zmenách a skutočnostiach, ktoré by mohli mať vplyv na práva a povinnosti vyplývajúce z tejto zmluvy v lehote najneskôr do 30 kalendárnych dní.

- 2) Zmeny a doplnenia zmluvy môžu byť vykonané len prostredníctvom písomných dodatkov podpísaných obidvoma zmluvnými stranami.

- 3) Zmluva je vyhotovená v šiestich origináloch, pričom každá zo zmluvných strán obdrží po tri exempláre.

- 4) Zmluva nadobúda platnosť dňom jej podpísania obidvoma zmluvnými stranami a účinnosť dňom nasledujúcom po jej zverejnení.

- 5) Prílohy k zmluve sú:

- a) Príloha 1: Dohoda o správe č. ENIAC-ED-27-09 uzavretá medzi spoločným podnikom a Ministerstvom školstva SR

- b) Príloha 2: Technická špecifikácia projektu Technical Annex to E2COGaN Energy Efficient Converters using GaN Power Devices

- c) Príloha 3: Špecifikácia projektu spoločného podniku

- d) Príloha 4: Rozpis celkových prostriedkov štátneho rozpočtu Slovenskej republiky na financovanie oprávnených nákladov projektu spoločného podniku v jednotlivých rokoch jeho riešenia

- e) Príloha 5: Predpokladaný rozpis celkových vlastných prostriedkov spolufinancovania NanoDesign, s.r.o. v projekte E2COGaN č. 324280/2012 spoločného podniku v jednotlivých rozpočtových rokoch jeho riešenia (v EUR).

| V Bratislave dňa                 | V Bratislave dňa          |

|----------------------------------|---------------------------|

|                                  |                           |

|                                  |                           |

|                                  |                           |

|                                  |                           |

| loc. PhDr. Dušan Čaplovič, DrSc. | Ing. Martin Daříček, PhD. |

| minister                         | štatutárny orgán          |

ENIAC-ED-27-09 Strana 1 z 8

Príloha č.1 k zmluve

### **Eniac JOINT UNDERTAKING**

# DOHODA O SPRÁVE MEDZI SPOLOČNÝM PODNIKOM ENIAC A MINISTERSTVOM ŠKOLSTVA SLOVENSKEJ REPUBLIKY

### 1. Zmluvné strany

Tento materiál ustanovuje dohodu medzi spoločným podnikom ENIAC (ďalej len "Spoločný podnik") a Ministerstvom školstva Slovenskej republiky (ďalej len "Národný financujúci orgán"), ktoré ustanovila Slovenská republika v súlade s čl.3 ods. 4 a čl. 12 a ods. 3 štatútu Spoločného podniku, ktorý je prílohou Nariadenia rady (EK) č. 72/2008 z 20. decembra 2007, a ktorým sa zakladá "Spoločný podnik ENIAC<sup>1</sup>". Dohodou sa stanovujú vzťahy medzi Spoločným podnikom a národnými financujúcimi orgánmi určenými členskými štátmi ENIAC pre administratívne zabezpečenie implementácie projektov a poskytovanie verejných prostriedkov.

### 2. Rozsah

Táto dohoda detailne stanovuje požiadavky kladené na obidve straty za účelom implementácie projektov vybraných Spoločným podnikom. Je potrebné ju vykonávať v súlade s Nariadením rady (EK) č. 72/2008, ktorým sa zakladá "Spoločný podnik ENIAC", výzvami Spoločného podniku na predkladanie návrhov projektov, rozpočtovými pravidlami Spoločného podniku podľa potreby a s členstvom Slovenskej republiky v Spoločnom podniku.

Táto dohoda je záväzná pre Spoločný podnik a Národný financujúci orgán ustanovený Slovenskou republikou.

### 3. Výklad tejto dohody

Národná financujúci orgán je povinná zabezpečiť výklad požiadaviek vyplývajúcich z tejto dohody a konať tak, aby umožnila implementácia projektov a poskytnutie verejných prostriedkov tak, ako je to stanovené v článku 12 odsek 3 štatútu Spoločného podniku.

Na zamedzenie nečestnému konaniu a podvodom je potrebné riadiť sa podľa Nariadenia Rady (EK, Euratom) č. 2988/95 zo dňa 18. decembra 1995 o ochrane finančných záujmov Európskych spoločenstiev<sup>2</sup>, Nariadenia Rady (EK, Euratom) č. 2185/96 zo dňa 11. novembra 1996 týkajúceho sa

\_

<sup>&</sup>lt;sup>1</sup> OJ L 30. 4.2.2008, str. 21

<sup>&</sup>lt;sup>2</sup> Ú. v. EÚ L 312, 23.12.1995, str. 1

ENIAC-ED-27-09 Strana **2** z **8**

kontrol na mieste a previerok uskutočňovaných Komisiou za účelom ochrany finančných záujmov Európskych spoločenstiev proti podvodom a iným nečestným konaniam<sup>3</sup> a Nariadenia (EK) č. 1073/1999 Európskeho parlamentu a Rady týkajúceho sa prešetrovaní ukončených Európskym úradom pre boj proti podvodom<sup>4</sup>.

Výrazy, ktoré sa použijú v tomto materiáli, majú rovnaký význam ako v Nariadení Rady (EK) č. 72/2008, ktorým sa zakladá "Spoločný podnik ENIAC", vo výzvach Spoločného podniku na predkladanie návrhov projektov a v rozpočtových pravidlách Spoločného podniku.

### 4. Národné zmluvy o grantoch

### a) Komunikácia o oprávnenosti národných kritérií

Národný financujúci orgán zabezpečí komunikáciu so Spoločným podnikom ohľadom oprávnenosti národných kritérií a iných zákonných a finančných požiadaviek platných pre každú výzvu na predkladanie návrhov projektov za účelom zostavenia národných zmlúv o grantoch s riešiteľmi projektu. Tieto kritériá a požiadavky budú predložené Spoločnému podniku ešte pred zverejnením výzvy na predloženie návrhov projektov Spoločnému podniku, a do 30 dní od požiadavky výkonného riaditeľa.

Odsúhlasené oprávnené národné kritéria budú v zmysle predchádzajúceho odseku začlenené do výzvy na predloženie návrhov projektov Spoločnému podniku.

Národný financujúci orgán uzatvorí zmluvy o grantoch s riešiteľmi projektov v súlade s vlastnými vnútroštátnymi predpismi s prihliadnutím na:

- (a) iba kritériá oprávnenosti, ktoré boli uvedené vo výzve alebo vo všetkých ďalších aktualizáciách výzvy;

- (b) iné zákonné a finančné požiadavky na zostavenie národných zmlúv o grantoch, ktoré stanovujú národné zákony a predpisy, a ktoré boli odkonzultované so Spoločným podnikom v uzávierke podľa predchádzajúceho odseku.

### b. Výber návrhov projektov

Spoločný podnik je zodpovedný za hodnotenie a výber návrhov projektov a za pridelenie verejných prostriedkov riešiteľom projektu podľa na výzvy na predkladanie návrhov projektov Spoločného podniku.

Predložené návrhy projektov sú posudzované nezávislými odborníkmi.

Rada verejných orgánov schváli zoznam vybraných návrhov projektov, doplnený údajmi o verejných prostriedkoch (Spoločného podniku a/alebo národného financujúceho orgánu) ako aj odporúčaniami na ďalšiu fázu rokovaní. Výkonný riaditeľ Spoločného podniku oznámi jednotlivým žiadateľom a Národnému financujúcemu orgánu tieto výsledky spoločne s bodovým hodnotením, pripomienkami a prípadnými odporúčaniami na zmeny do 15 dní od uskutočnenia výberu.

\_

<sup>&</sup>lt;sup>3</sup> Ú. v. EÚ L 295, 15.11.1996, str. 2

<sup>&</sup>lt;sup>4</sup> Ú. v. EÚ L 139, 31.05.1999, str. 1

ENIAC-ED-27-09 Strana **3** z **8**

Na základe tejto komunikácie a v zmysle zoznamu vybraných návrhov projektov, ktoré schválila Rada verejných orgánov, začne Spoločný podnik v zastúpení výkonným riaditeľom technické rokovania s cieľom schváliť "Technickú špecifikáciu projektu<sup>5</sup>" v rámci limitov vyjednávacieho mandátu a finančných zdrojov na riešiteľa projektu podľa rozhodnutia Rady verejných orgánov.

- V prípade, že boli technické rokovania úspešne ukončené, výkonný riaditeľ predloží ich výsledky spoločne s kompletnou príslušnou dokumentáciou riadiacej rade a Národnému financujúcemu orgánu za účelom vypracovania národnej zmluvy o grante.

- V prípade zmien, ktoré nemôže mandát Rady verejných orgánov vopred predpokladať alebo v prípade neúspešných technických rokovaní, výkonný riaditeľ predloží na schválenie Rade verejných orgánov výsledky rokovaní spoločne zo žiadosťou o zmenu projektu. Rozhodnutie Rady verejných orgánov predloží výkonný riaditeľ riadiacej rade a Národnému financujúcemu orgánu spoločne s kompletnou príslušnou dokumentáciou, aby mohla byť vypracovaná národnej zmluva o grante.

Po ukončení rokovaní predloží Spoločný podnik koordinátorovi zvoleného konzorcia na podpis zmluvu o grante Spoločného podniku a prístupové podklady.

### c) Vypracovanie národných zmlúv o grantoch

Po ukončení výberového konania a rokovania, ktoré uskutočnil Spoločný podnik, Národný financujúci orgán vypracuje spoločne s riešiteľmi projektov národné zmluvy o grantoch. Národné zmluvy o grantoch budú zostavované v súlade s pravidlami Národného financujúceho orgánu, aj v prípade, že žiadne národné verejné prostriedky nie sú zabezpečené Radou verejných orgánov predovšetkým, čo sa týka kritérií oprávnenosti a iných nevyhnutných finančných a právnych požiadaviek, okrem prípadov kedy nie je možné vypracovať národnú zmluvu o grante z dôvodu nesplnenia národných kritérií oprávnenosti zo strany riešiteľa projektu alebo iných finančných a zákonných požiadaviek.

Finálna schválená "technická špecifikácia projektu" vyplývajúca z rokovacieho procesu uskutočneného Spoločným podnikom bude rovnaká<sup>6</sup> pre vypracovanie národných zmlúv o grantoch k tomu istému projektu vo všetkých členských štátoch ENIAC.

Dátum začiatku a trvania projektu bude špecifikovaný v "technickej špecifikácii projektu". Národné zmluvy o grantoch stanovujú oprávnené náklady, ktoré budú poskytované odo dňa začatia riešenia projektu nezávisle od dátumu ich podpísania.

<sup>&</sup>lt;sup>5</sup> "Technická špecifikácia projektu" predstavuje technický materiál, ktorý čo najjasnejšie a stručne popisuje všetky činnosti, aktivity a úlohy, ku ktorým sa účastníci projektu zaviazali a spĺňajú vedecké a výskumné ciele stanovené v zmluvách o grantoch. Východiskom je popis vedeckých/technologických cieľov a pracovných plánov načrtnutých v návrhu projektu, ktoré sa v priebehu hodnotenia a počas ďalších rokovaní o zmluve eventuálne upravia na základe špecifických odporúčaní externých znalcov. Okrem tejto jej právnej závažnosti "technická špecifikácia projektu" slúži pre príjemcov grantu, Spoločný podnik, Národný financujúci orgán a eventuálne pre externých znalcov ako referenčný údaj, aby mohli efektívne sledovať a kontrolovať napredovanie daného projektu počas celého jeho trvania.

<sup>&</sup>lt;sup>6</sup> okrem prekladov, ak je to potrebné

ENIAC-ED-27-09 Strana **4** z **8**

Národný financujúci orgán zabezpečí, aby ustanovenia národnej zmluvy o grante boli v súlade s článkom 107 odseku 1 rozpočtových pravidiel ENIAC, ktoré uvádzajú, že ak si riešenie projektu vyžaduje, aby príjemca uskutočnil verejné obstarávanie, musí požiadavku vo výberovom konaní formulovať na základe najlepšej ponúknutej ceny, t.j. vo výberovom konaní ponúkne najlepší pomer ceny a kvality, pričom sa snaží vyhnúť konfliktu záujmov.

Národný financujúci orgán vynaloží maximálne úsilie, aby urýchlil svoje interné postupy na uzatvorenie národných zmlúv o grante. Národná zmluva o grante musí byť podpísaná najneskôr do 30 dní od ukončenia rokovaní, ktoré uskutočnil Spoločný podnik (ENIAC).

Národný financujúci orgán bude informovať Spoločný podnik o podpise národnej zmluvy o grante a kópiu národnej zmluvy o grante predloží Spoločnému podniku do 15 dní odo dňa jej podpisu jej príjemcom.

Následne bude Spoločný podnik informovať Národný financujúci orgán o podpísaní zmluvy o grante medzi Spoločným podnikom a príjemcom a kópiu tejto zmluvy o grante mu predloží do 15 dní odo dňa jej podpisu.

Zmluva o grante Spoločného podniku nadobúda platnosť po pripojení sa minimálne troch neprepojených subjektov, ktoré boli založené v minimálne troch členských krajinách Spoločného podniku v deň pripojenia sa posledného z nich.

### d) Technický monitoring

Spoločný podnik je zodpovedný za monitorovanie riešenia projektu v súlade s "Technickou špecifikáciou projektu".

Konzorcium predloží Spoločnému podniku svoju technickú správu(y)<sup>7</sup> a výstupy v termínoch, ktoré sú na predloženie správ stanovené v "Technickej špecifikácii projektu" a zmluve o grante uzavretej medzi Spoločným podnikom a riešiteľmi projektu.

Spoločný podnik poskytne technické správy a výsledky technického hodnotenia riešenia projektu ním vykonané Národnému financujúcemu orgánu do 15 dní po ich schválení a potvrdení výkonným riaditeľom.

Technické hodnotenie riešenia projektu vypracované Spoločným podnikom zohľadní v prípade potreby špecifické požiadavky danej krajiny navrhnuté Národným financujúcim orgánom, ktoré Národný financujúci orgán potrebuje pre akceptovanie úhrady nákladov príjemcov grantov.

Národný financujúci orgán nebude požadovať ďalšie dodatočné technické správy okrem tých, ktoré požaduje Spoločný podnik.

Správy, ktoré sú predkladané Spoločnému podniku, sú vyhotovené v anglickom jazyku.

.

<sup>&</sup>lt;sup>7</sup> Technická správa pozostáva z prehľadu o napredovaní prác pre dosiahnutie cieľov projektu, vrátanie úspechov a dosiahnutí míľnikov a výstupov stanovených v "Technickej špecifikácii projektu" a rozdielov medzi očakávanými a skutočne zrealizovanými činnosťami. Technická správa(y) obsahuje aj informácie o riadení (manažovaní) projektu a upravenú verziu plánov pre jeho využívanie a zverejňovanie.

ENIAC-ED-27-09 Strana 5 z 8

### e) Finančný monitoring/Platby

Národný financujúci orgán spracuje požiadavky na úhradu nákladov príjemcov grantov v ich vlastnom jazyku podľa vlastných postupov danej krajiny a zohľadní výsledky technického monitoringu, ktorý uskutočnil Spoločný podnik. Zabezpečí, aby boli nároky platné a náklady oprávnené a v súlade s národnou zmluvou o grante. Všetky ostatné potrebné kontrolné činnosti spadajú do kompetencie Národného financujúceho orgánu.

Prípadne Národný financujúci orgán zrealizuje platby z prostriedkov štátneho rozpočtu priamo príjemcom podľa národných zmlúv o grantoch.

Národný financujúci orgán potvrdí Spoločnému podniku výšku akceptovaných nákladov, iných finančných alebo zmluvných oblastí týkajúcich sa plnenia národnej zmluvy o grante a prípadne aj každú platbu uskutočnenú voči príjemcovi grantu. Národný financujúci orgán pošle toto potvrdenie Spoločnému podniku do 15 dní od jeho realizácie. Národný financujúci orgán zabezpečí realizáciu finančného a zmluvného monitoringu výlučne v zmysle národných predpisov a postupov.

Príslušne Spoločný podnik zrealizuje úhradu svojho príspevku príjemcom grantu do 30 dní od dňa prijatia hore uvedeného potvrdenia od Národného financujúceho orgánu.

Národný financujúci orgán bude zabezpečovať evidenciu platieb príjemcom grantov. Národný financujúci orgán obdrží informácie o príslušnom finančnom monitoringu vykonanom Spoločným podnikom.

Spoločný podnik a Národný financujúci orgán súhlasia s poskytovaním si dôkazov o platbách uskutočnených pri plnení príslušných zmlúv o grantoch predložením kópie prevodného príkazu na žiadosť druhej strany.

Každá strana upovedomí druhú stranu o prípade, že dôjde k zdržaniu alebo zníženiu platby v dôsledku neuspokojivého konania príjemcu alebo z iného dôvodu zdržania platby najneskôr do 15 dní od jeho zistenia.

### 5. Právo na zaplatenie

Každá strana upovedomí písomne druhú stranu hneď ako zistí, že príjemca porušil zmluvu o grante uzavretú s touto stranou ako aj povinnosť použiť prostriedky štátneho rozpočtu na vopred stanovený účel. V prípade grantov, ktoré podliehajú právu na zaplatenie, je nevyhnutné uchovávať dokumenty zodpovedajúce uplatňovaniu tohto práva (napr. dohody a záznamy o platbách) po dobu eventuálneho vymáhania.

### 6. Dodatky a ukončenie zmlúv o grantoch

Je v zodpovednosti každej strany upozorniť druhú stranu, že považuje jej konanie za neadekvátne a chce v platbách grantov uskutočniť zodpovedajúcu zmenu pre ich pokračovanie na základe dodatku alebo ukončiť zmluvu o grante.

ENIAC-ED-27-09 Strana **6** z **8**

V prípade že je potrebné v " Technickej špecifikácii projektu" uskutočniť podstatnú zmenu, Spoločný podnik bude informovať Národný financujúci orgán o účele dodatku. Národný financujúci orgán predloží Spoločnému podniku špecifické požiadavky svojej krajiny najneskôr do 15 dní od získania tejto informácie. Novú "Technickú špecializáciu projektu" prerokuje Spoločný podnik po zohľadnení všetkých požiadaviek Národného financujúceho orgánu. Spoločný podnik oznámi Národnému financujúcemu orgánu aktualizovanú verziu "Technickej špecifikácie projektu" do 15 dní od ukončenia tohto rokovania.

Akýkoľvek iný dodatok "Technickej špecifikácie projektu" prerokuje Spoločný podnik, ktorý oznámi Národnému financujúcemu orgánu zmenu "Technickej špecifikácie projektu" do 15 dní od ukončenia tohto rokovania.

Do 15 dní je Spoločný podnik zodpovedný informovať Národný financujúci orgán o akejkoľvek zmene alebo ukončení zmluvy o grante medzi Spoločným podnikom a príjemcom.

Do 15 dní je Národný financujúci orgán zodpovedný informovať Spoločný podnik o akejkoľvek zmene alebo ukončení zmluvy o grante medzi Národným financujúcim orgánom a príjemcom.

### 7. Audity – kontroly

Spoločný podnik bude u príjemcov verejných finančných prostriedkov Spoločného podniku uskutočňovať kontroly na mieste a finančné audity. Tieto kontroly a audity bude vykonávať buď priamo Spoločný podnik alebo Národný financujúci orgán v mene Spoločného podniku na základe žiadosti Spoločného podniku. Národný financujúci orgán môže na vykonanie kontrol a auditov menovať externý orgán, ktorý tak urobí v jeho mene. Národný financujúci orgán je oprávnený uskutočniť u príjemcov prostriedkov štátneho rozpočtu iné kontroly a audity, v prípade že to považuje za nevyhnutné a Spoločný podnik oboznámi s ich výsledkami.

Obidve strany sa budú vzájomne informovať o začatí ako aj o výsledkoch všetkých kontrol a auditov ustanovených v zmysle predchádzajúceho odseku, a to do 15 dní.

### 8. Politika práv duševného vlastníctva

Pre účely národných zmlúv o grantoch v rámci tejto zmluvy a bez toho, aby boli dotknuté pravidlá hospodárskej súťaže Spoločenstva, prednosť majú ustanovenia o duševnom vlastníctve schválené Nariadením Rady (EK) č. 72/2008 pred vnútroštátnymi predpismi, pravidlami o poskytovaní grantov alebo projektami súvisiacimi s duševným vlastníctvom.

### 9. Dôverné informácie

Všetky informácie, ktoré príslušná strana získa v súvislosti s touto dohodou, sa budú považovať za dôverné a každá strana súhlasí, že:

- (a) bude dôverné informácie chrániť zodpovedajúcim a adekvátnym spôsobom v súlade s platnými odbornými štandardami;

- (b) bude dôverné informácie používať a reprodukovať len na účely stanovené v tejto dohode;

ENIAC-ED-27-09 Strana **7** z **8**

(c) nebude zverejňovať alebo iným spôsobom poskytovať dôverné informácie iným osobám ako tým, ktoré tieto informácie potrebujú na splnenie účelu stanoveného v tejto dohode.

Predchádzajúci odsek sa nebude vzťahovať na informácie,

- (a) ktoré sú verejne známe; alebo

- (b) ktoré prijímacia strana už pozná;

- (c) keď je zverejnenie dôverných informácií požadované národným zákonom.

#### 10. Administratívne záležitosti

Zúčastnené strany tejto dohody si budú uchovávať a aktualizovať zoznam kontaktných osôb zodpovedných za vybavovanie záležitostí týkajúcich sa tejto dohody.

Obidve strany sa budú vzájomne informovať o iných osobách, ktoré sú zodpovedné za príslušnú uzavretú zmluvu o grante.

Kompletná komunikácia medzi stranami sa uskutočňuje v anglickom jazyku<sup>8</sup>.

Kompletná písomná komunikácia medzi zúčastnenými stranami tejto dohody bude prípadne uvádzať názov zmluvy a identifikačné číslo (Národného financujúceho orgánu /alebo Spoločného podniku). Každá strana bude druhej strane odpovedať na otázky týkajúce sa tejto dohody najneskôr do 7 pracovných dní. V prípade, že druhá strana nedostane žiadnu odpoveď ani do 15 dní, bude sa to považovať za kladnú odpoveď.

### 11. Práva kontroly Európskej komisie, OLAF a Dvora audítorov

V súvislosti s touto dohodou zabezpečia obidve strany uplatňovanie kontrolných práv Európskej komisia, Európskeho úradu pre boj proti podvodom a/alebo Dvora audítorov podľa článku 12 odseku 5 a článku 12 odseku 6 Nariadenia rady (EK) č. 72/2008.

### 12. Riešenie sporov

Súd prvého stupňa alebo odvolací súd, Súdny dvor Európskych spoločenstiev má výlučnú súdnu právomoc pri riešení súdnych sporov medzi Spoločným podnikom a Národným financujúcim orgánom, ktoré sa týkajú výkladu, uplatnenia alebo platnosti tejto dohody.

### 13. Trvanie dohody

Táto dohoda nadobudne platnosť v deň jej podpísania oboma stranami dohody a bude platná počas obdobia členstva Slovenskej republiky v Spoločnom podniku. Túto dohodu možno kedykoľvek meniť na základne vzájomného písomného súhlasu zúčastnených strán. Táto dohoda nezahŕňa teraz alebo

<sup>8</sup> V prípade, že je nevyhnutné podpísať pôvodné materiály, ktoré Národná grantová organizácia vyhotovuje v domácom jazyku, Národná grantová organizácia ich predloží spoločne s prekladom do anglického jazyka.

ENIAC-ED-27-09 Strana **8** z **8**

v budúcnosti žiadnu výmenu finančných prostriedkov, ani vytvorenie akéhokoľvek záväzku voči časti akejkoľvek strany na vykonanie úhrady voči inej strane.

Táto dohoda pozostáva z úplnej dohody uzavretej medzi zúčastnenými stranami na stanovený účel a jej úpravy alebo dodatky platia len po uvedení a priložení podpisov obidvoch strán tejto dohody.

Vyhotovené v Bruseli v dvoch kópiách

za Spoločný podnik za Ministerstvo školstva Slovenskej republiky

vlastnoručný podpis vlastnoručný podpis

Dirk Beernaert p. Marta Cimbáková

dočasný výkonný riaditeľ riaditeľka odboru štátnej a európskej politiky

vo vede a technike

Úsek vedy a techniky

# ENIAC JOINT UNDERTAKING TECHNICAL ANNEX

# E<sup>2</sup>COGaN – Energy Efficient Converters using GaN Power Devices

**ENIAC Call 2012 - 1**

| Project acronym                       | E <sup>2</sup> COGaN                                                                                               |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Project full title                    | Energy Efficient Converters using GaN Power Devices                                                                |

| Sub Programme, in order of importance | 3. Energy Efficiency                                                                                               |

| of importance                         | 3.2 Energy Distribution and Management – Smart Grid Energy Efficiency >> 90% (solar inverter / EV battery charger) |

|                                       | 1.1 Intelligent Electrical Vehicle                                                                                 |

|                                       | Energy efficiency and CO2 reduction through smart interconnections                                                 |

|                                       | 3.1 Sustainable and efficient energy generation                                                                    |

|                                       | Energy efficiency >> 90%, reliability and lifetime (solar inverter)                                                |

|                                       | 8. Equipment, Materials and Manufacturing                                                                          |

|                                       | 8.2 More than Moore                                                                                                |

|                                       | GaN power technology addressing new functionalities                                                                |

| Version of Technical Annex            | TA version 1.0                                                                                                     |

| Date of Technical Annex               | 29/11/2012                                                                                                         |

|                                       |                                                                                                                    |

| Start Date of Project                 | 01/04/2013                                                                                                         |

| Duration of project                   | 36months                                                                                                           |

| Maximum JU funding                    | 3,940,787.00€                                                                                                      |

| Coordinator                           | ON Semiconductor Belgium BVBA                                                                                      |

| Project coordinator                   | Frederik Deleu                                                                                                     |

| Tel                                   | +32 55 332932 / +32 499 596103                                                                                     |

| Email                                 | frederik.deleu@onsemi.com                                                                                          |

# 2 HISTORY OF TECHNICAL ANNEX LATER ANNEX 1 TO THE JU GA

| Version<br>Number | Date       | Main changes / Amendment number | Description                                                                                          |

|-------------------|------------|---------------------------------|------------------------------------------------------------------------------------------------------|

| 0.1               | 15/11/2012 | First draft                     | Copy of FPP into TA template; apply changes of coordinator, WP2 leader, DEA-LETI contribution;       |

| 0.2               | 23/11/12   | Minor changes                   | Change contribution of NXP-B to WP7; add explanation to table 2; add explanation on resource section |

| 0.3               | 27/11/12   | Content update                  | State-of-the-art updates, standards and IP management.                                               |

| 0.4               | 28/11/12   | Content update                  | Complete specification table, add information on subcontract cost, add comment about standards.      |

| 1.0               | 28/11/12   | End of negotiations             |                                                                                                      |

## 3 PUBLISHABLE PROJECT SUMMARY

Efficient power conversion systems are at the heart of the worldwide effort for a green economy, since they can minimize losses and save energy and contribute thus to achieve a better CO<sub>2</sub> balance sheet. Semiconductor power devices are a central part of any power conversion circuit and are ubiquitous in our daily lives: they transform voltages for a multitude of appliances, such as from the 220V AC mains to a 12V DC end-user appliance and enable to convert from DC (such as a battery in an electric car) to AC (such as a motor drive) and vice versa. The importance and the key role of power conversion systems are especially significant in cases where operation relies on battery or limited renewable energy sources where they are a key element of the overall efficiency of the system. Hence, highly efficient power switching devices are a key for successful introduction of full electric vehicles into the market.

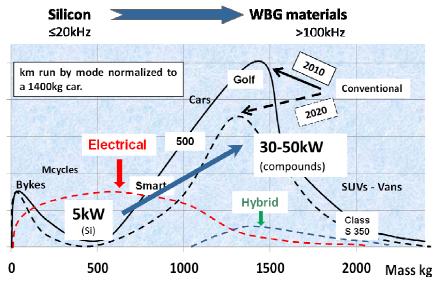

Traditionally, high voltage (>400V) power switches are made in silicon. Several major breakthroughs in silicon power device architectures have been accomplished (IGBT, superjunction) over the past 30 years. However, due to the intrinsic properties of silicon (relatively low bandgap, limited thermal conductivity, etc), advances have slowed down. Further performance improvements and higher efficiencies will become more and more challenging and cost-intensive to achieve. This is the driving motivation why the industry is currently investing in the research and development of disruptive power device technologies, as based on the Wide-Band Gap (WBG) materials GaN and SiC, to replace the incumbent Si technologies with the mission to achieve a higher performance at equivalent cost.

Both SiC and GaN present a band gap of about 3.3eV and an associated critical field of about 3 MV/cm - 10 times higher than in Si – enabling to decrease considerably the total chip area at equivalent high voltage and on-state resistance. The current designs mainly rely on unipolar structures (FET-based switches and Schottky-barrier diodes) having very low switching losses and practically no reverse recovery energy. These properties allow stepping the switching frequency to higher levels, enabling a massive reduction of passive elements like inductors and capacitors. The wide band gap also makes WBG-based devices intrinsically interesting for the use in harsh environments under high temperatures, making them a strong contender for the automotive market. SiC diodes are for instance commercially available, with the first switches being currently introduced. SiC power electronics is however still hampered by a severe cost penalty of the SiC starting material.

Boosted by the widespread use of GaN in optoelectronics – GaN is the starting material for blue and green emitting (laser) diodes – GaN electronic devices have been developed starting from radar and RF for military and aerospace applications. Recent advances in the challenging epitaxy of GaN on silicon starting substrates triggered the investigation of GaN for the high volume market of power conversion.

The advances in the GaN-on-Si technology promise for the first time to bring down the cost of a high-performance wide-band-gap power technology to silicon cost level. We foresee a dominant position by the end of this decade in power converters for electrical vehicles and photovoltaic systems.

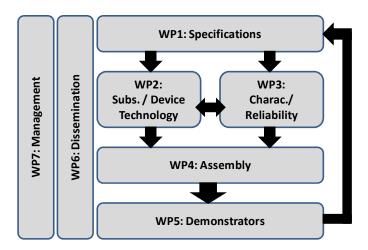

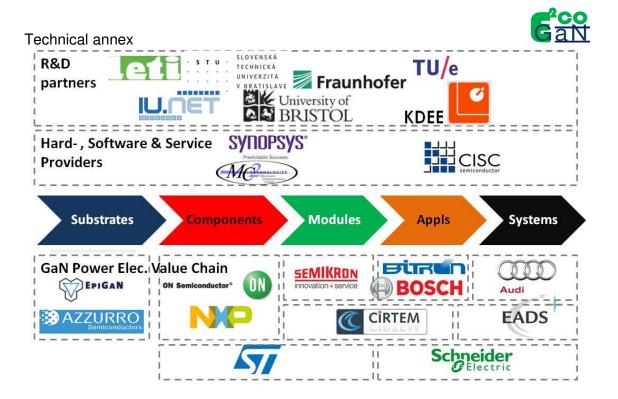

This project will target the demonstration of GaN-on-Si as a disruptive High Voltage (HV) technology (Schottky Barrier Diodes (SBDs) and High Electron Mobility Transistors (HEMTs)) through the whole value chain up to demonstrators with high industrial, societal and environmental relevance. More precisely the character will be proven through a well-balanced and application specific trade-off between the "corner" benefits given by higher efficiency, higher switching frequency, smaller footprint and weight and competitive cost on system level with respect to Si or SiC. The consortium is set up in order to provide a common and global, industry-relevant approach implying the whole GaN power electronics value chain from the substrate provider, GaN device manufacturer, assembly house to the end user, completed by

top academic institutes and other tool or service providers (simulation software, measurement tools, etc.). Concerning the GaN power devices the plan is to start with 600V, 10A and gradually explore higher voltages (up to 1500V) and currents (up to 100A) towards the end of the project, giving priority to the early exploration of applications below 10kW.

Special attention will be paid on reliability issues and parasitic effects that will be investigated through a combined approach based on advanced electro/optical measurements and electro/thermo/mechanical TCAD simulations allowing to understand and identify the Safe Operating Area and to develop a robust and reliable GaN-on-Si power device technology platform.

Another important topic is the development of suitable packages / modules allowing high frequency and/or high temperature operation together with the design and implementation of the associated gate drivers.

Finally, the project demonstrators will focus on two application domains with strategic relevance:

First, on Photovoltaic (PV), where the use of GaN will be explored in micro-grid interfacing circuits evaluating an overall gain in system efficiency and operating cost over incumbent Si- or competing SiC-based solutions.

Second, on Automotive, where the benefit of GaN will be investigated in grid-connected chargers for high voltage batteries, as found in new hybrid and full electric vehicles. Power conversion for interfacing to lower voltage levels will also be investigated. Main motivations are gain in efficiency, weight, footprint and – related to the expected high temperature operation capacity – ease in the heat and cooling management.

Moreover, the project will include a pre-study in Aeronautics with specific high temperature (250 ℃) mission profiles as well as the atmospheric radiation constraint.

Among the foreseen potential societal and environmental impact of this project are the establishment of a pan-European GaN power electronics technology ecosystem and competence ensuring the autonomy of Europe on strategic and disruptive semiconductor and power conversion technologies, the contribution to higher efficiency in both energy generation and usage and last, but not least, a significant step towards a knowledge-based, resource efficient, low carbon European industry and economy.

# 4 RELEVANCE AND CONTRIBUTIONS TO THE CONTENT AND OBJECTIVES OF THE CALL

One of the EU's major goals for 2020 is to cut the CO<sub>2</sub> emissions of more than 20% with respect to 1990 values, while ensuring a sustainable growth based on a knowledge-based economy. This implicitly requires a resource-efficient industry, which is one of the major EU challenges for the beginning of the 21<sup>st</sup> century.

In order to reach this objective of a resource-efficient industry, private and public actors have to review the whole chain of energy generation (including thus a high proportion of renewable energies), distribution (e.g. via smart grids) and storage (e.g. batteries) and find new ways and technologies to avoid losses where ever possible. Very much related, electrical transport will need to be built out in order to replace or reduce the use of a low-efficient combustion engine by more efficient and cleaner sources of energy.

A crucial element in the overall energy efficiency is the efficiency of the power conversion steps. Power conversion is omnipresent all the way from the electricity provider to the end consumer and occurs basically at any utility interface. To give two examples, which are also chosen as demonstrators in the E²COGaN proposal: power conversion will ensure the energy injection from solar modules into the grid via a DC/AC converter and power conversion will allow us to charge the battery of an electrical vehicle via an appropriate converter once connected to the mains.

Due to the multitude of power conversion steps along the distribution chain, the gain of 1% in efficiency at one level can already make a huge difference in the overall efficiency of the system.

So far, technologists lacked a solution that could give a good trade-off between performance and costs along the value chain from die to system level. Silicon high voltage devices (IGBTs, Superjunction) are reasonably priced, but have already reached their performance scalability limit. For what concerns SiC power devices, they have already shown their potential of higher efficiency for both diodes and transistors, but prices are high and are not likely to decrease in the near future due to the expensive substrates, thus hindering a broader market entry and wider use.

In this respect, GaN power devices can be seen as a revolutionary technology: they have the unique potential to combine both an appealing price roadmap —GaN starting substrates will decrease in price with the optimization of GaN growth on Si using multi-wafer epitaxy tools while device production will be carried out in conventional silicon manufacturing lines — and high performances being equal or better to state-of-the-art SiC devices in the 600V -1200V range and by far better than incumbent Si technologies on die level. Regarding the final applications at the top of the value chain, further advantages appear related to their capability of higher switching frequencies and higher temperature operation. Application designers will thus be able to reduce the size of passive components needed on system level (such as inductors and capacitors) or even the cooling requirements, giving benefits in terms of system cost and foot print thus enabling further integration.

In this project we will demonstrate the high potential of GaN power devices through the whole value chain up to relevant applications with societal impact: in photovoltaic via inverters with higher efficiency and lower cost, in automotive via battery chargers and HV/LV DC/DC converters with compact and cost effective design.

More precisely, this proposal will provide relevant solutions to 3 of the 8 domains and 4 of the 25 grand challenges as listed in the latest Annual Work Plan (AWP) 2012: to the Grand Challenge 1 "Intelligent vehicle" of Domain 1 "Automotive and Transport", to the Grand Challenges 1 "Sustainable and efficient energy generation" and 2 "Energy distribution and management – smart grid" of Domain 3 "Energy Efficiency" and finally to Grand Challenge 2 "More than Moore" of Domain 8 "Equipment, Materials and Manufacturing".

The E²COGaN project has the highest compliance level with the Grand Challenge 3.2 "Energy Efficiency - Energy distribution and management – smart grid" which covers thematically the main GaN-device based application demonstrators such as the solar inverter – feeding electricity into the grid – and the electric vehicle battery charger – storing the electricity provided by the grid for further use in transport.

Moreover, the E<sup>2</sup>COGaN project has a high compliance level with the Grand Challenge 1.1 "Automotive and Transport – Intelligent Vehicle" mapping out new ways of enabling technologies for electric cars in terms of highly efficient battery charging and overall power management. It is also strongly related to Grand Challenge 3.1 "Energy Efficiency - Sustainable and efficient energy generation" aiming to achieve higher efficiency solar inverters based on GaN power devices while including cost aspects and lifetime constraints, contributing thus to reduce the overall losses between the generation of renewable energies and its usage by the end customer.

The project furthermore contributes to a sustainable European semiconductor industry for the globalization era: GaN devices as an emerging technology with increasing world-wide demand will be produced in existing European 6" and 8" Si production facilities whose existence otherwise would be threatened by the gradual out-phasing of incumbent silicon technologies (moving to larger wafer sizes or even ceasing production) making thus the best use of existing European manufacturing infrastructure in terms of facilities, tools and competences, which is completely in line with the Grand Challenge 8.3 "Equipment, Materials and Manufacturing - More than Moore".

### 5 R&D INNOVATION AND TECHNICAL EXCELLENCE

Efficient power conversion systems are at the heart of the worldwide effort for a green economy, since they can minimize losses and save energy and contribute thus to achieve a better CO<sub>2</sub> balance sheet. Semiconductor power devices are a central part of any power conversion circuit or module and are ubiquitous in our daily lives: they transform voltages for any kind of appliances, such as from the 220 V AC mains to a 12 V DC end-user appliance and enable to convert DC (such as a battery in an electric car or PV modules) to AC (such as a motor drive and grid) and vice-versa (in the case of chargers). The importance and the key role of power conversion systems are especially significant in cases where operation relies on battery or limited renewable energy sources where they are a key element of the overall efficiency of the system.

The general concept of this project is to develop the next generation of power electronic devices based on a scalable, cost-effective, high-performance and reliable GaN-on-Si device technology platform which will provide discrete and integrated devices suitable for 600 V and higher (up to 1.2 kV) and to prove its benefits at application level in photovoltaic systems and full electric vehicles. To be successful, the complete value chain from wafer suppliers, IDMs, module makers to end-users has to be considered involving competences from large industrial partners, SMEs and institutes and academics. The project aims to validate the emerging and revolutionary GaN HV technology from wafer levels to relevant end products thus putting Europe at the forefront of both energy efficient power conversion efforts and an innovative GaN power electronics ecosystem.

### 5.1 GaN-on-Si Power Devices

### (a) State of the art

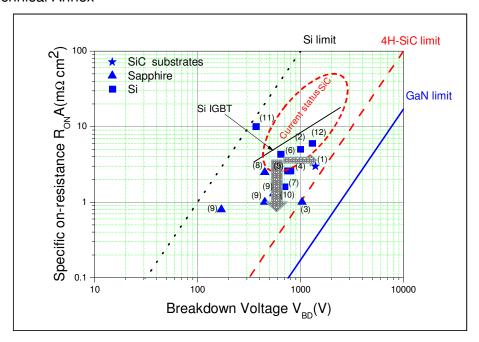

The specific on-resistance  $R_{ON}^*A$  as a function of breakdown voltage  $V_{BD}$  is the most widely used figure of merit to characterize the device performance since it determines the conduction losses and to some extent the switching losses of the device. Generally speaking, lower  $R_{ON}^*A$  leads to more efficient devices suitable for operation at higher frequencies. A summary of the state of the art results for GaN is given Figure 1.

The first thing to notice is that in terms of materials parameters, GaN is theoretically superior to all other competitor devices. As today, SiC seems to be more suitable for voltages higher than 1000 V while GaN is more suitable for voltages below 1000 V presenting the advantage of lower  $R_{ON}^*A$  at equivalent  $V_{BD}$ . It is interesting to note that the best results are obtained with GaN devices grown on sapphire substrates (triangle symbols) featuring state of the art values of  $R_{ON}^*A$  ~1 m $\Omega$ cm<sup>2</sup>.

Furthermore, GaN shows excellent switching behaviour in Schottky diodes ( $Q_{RR}$  comparable to that of SiC ) and in GaN HEMTs (the switching charge  $Q_{GD}$  being 10 times smaller than in a comparable Si device).

Figure 1: Summary of the state of the art RON vs VBD. The symbols represent experimental results for GaN HFET devices on different substrates  $Si(\blacksquare)$ , Sapphire ( $\blacktriangle$ ) and SiC (\*). The lines represent the theoretical limits for Si, SiC and GaN devices determined from fundamental materials properties. The dashed ellipse represents the current status of SiC devices. The thick and thin arrows represent the project target towards lower  $R_{ON}$  and higher  $V_{BD}$ , respectively.

However, many issues still remain and have to be understood and solved in a concerted manner before aiming any market introduction. Unless using an insulated gate, GaN HEMTs tend to be leaky ( $I_{OFF} = 100~\mu A/mm$ ) compared to Si devices. Also, they are sensitive to self-heating due to their comparatively small size and large current density. Moreover, the complex epitaxy structure forming the HEMT device is sensitive to trapping phenomena in the different layers or their interfaces that can influence the switching behaviour (gate or drain lag) or even degrade the basic device parameters ( $R_{ON}$ ,  $V_T$ ,  $I_{ON}$ ,  $I_{OFF}$ ). As a wide band gap material, GaN is considered to bring higher temperature robustness, but this will need to be proven on realistic HV devices.

In addition, most of the work focus is on GaN devices at voltages around 600 V which fulfils the requirements for several power applications; only very few reports have demonstrated devices operating higher than 1000 V. Moreover, most of the reported results have been obtained on wafer sizes of 100mm or smaller and based on III-V process integration flows, This, however, is incompatible with the objective of low-cost, high volume manufacturing to achieve maximum market penetration, that will require larger wafer sizes (150 or even 200mm) and the best use of existing silicon production know-how and facilities. Finally, most of the work presented in Figure 1 describes device performance characteristics without systematic reliability studies. All of the aforementioned call for further improvements to take full advantage of GaN potential superiority.

However, despite all the promising performances, the AlGaN/GaN power devices still suffer from various limiting factors that can be grouped as: i) parasitic and ii) reliability issues. These parasitic and reliability aspects have not yet been largely investigated. In particular, the multiple effects of highly energetic carriers (hot-electrons), high electric field and high power densities, present within the device active area, require an in-depth investigation and understanding in order to design and to develop a robust and reliable GaN device platform.

### (b) Advances beyond the state of the art

Figure 1 shows how GaN can be improved significantly at least up to the theoretical limit (thick solid line). This would require large efforts aiming to decrease  $R_{\text{ON}}^*A$  and to simultaneously increase the breakdown voltage. Here in this project we will mainly focus on the improvement of  $R_{\text{ON}}^*A$  (thick vertical arrow) for 600 V devices devoting also a smaller exploratory effort toward higher voltages up to 1500 V (thin horizontal arrow). Aim is to maintain good performance or even advances beyond the state of the art while extending the technology to large area up to 200 mm Si wafers in CMOS compatible process. To achieve this, the material quality will be improved through epitaxy, Au-free contacts and normally-off enhancement mode architectures.

In addition, to exploit the full potential of GaN HV devices while challenging incumbent Si and competing SiC technologies, it is mandatory to provide both a deeper and broader look on their intrinsic and parasitic physics and understand how it relates to potential use in applications. A considerable effort of the E²COGaN project will be spent to provide these answers through all kinds of electrical characterizations on wafer, packaged device and module level via DC and AC measurements, but also complementary and innovative analysis techniques such as IR for thermal mapping, DLTS for trap density and energy level scanning and electroluminescence for mapping of hot electrons. This will be complemented with reliability investigations.

# 5.2 Power Module Assembly and System Integration of GaN Power Devices

### (a) State of the art

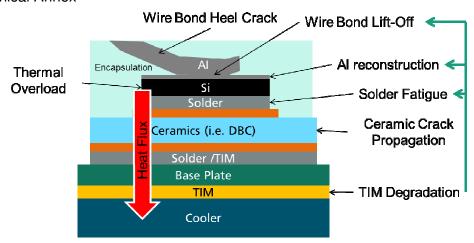

Classical Si power devices consist of a top side die contact realised with Al-wire bonds and a backside contact to the ceramic substrate (i.e. DBC) realised with solder (see Figure 2). The ceramic substrate itself is bonded to the base plate of the module, which is filled with an encapsulant (i.e. silicone). In the end application the module is mounted to a water cooler, where the thermal contact is enabled by a thermal interface material (TIM, i.e. grease, paste, foil, pad ...).

R&D on packaging of power devices has been mainly challenged by achieving good electromagnetic compatibility and good thermal heat dissipation in order to reach good system performance, while price and size need to be kept in a reasonable range. At the same time the package needs to deal with different coefficients of thermal expansion (CTE) of the materials used for packaging. Due to the varying loads leading to many temperature changes this issue is the main limiting factor to achieve long lifetimes.

Consequently current R&D activities are focussed on finding new technologies in order to reduce thermal resistance and increase the life time.

Figure 2: Classical structure of a power module with indication of the main heat path and failure mechanisms.

Besides the assembly of the power devices the gate control has an important influence on the overall efficiency of a power module. GaN power devices offer new perspectives in converter efficiency with at the same time challenging requirements for the gate driver.

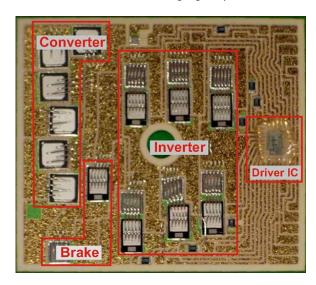

Figure 3: Example for system integration in a module today: A 3-phase rectifier bridge (converter: 600V Si-diodes), a 3-phase inverter (600V Si-IGBT and freewheeling diodes (FWD)), a brake-chopper (600V Si-IGBT and FWD), the gate-driver for all 7 switches and several sensors and SMD-components are compact assembled (soldered and bonded) on a ceramic substrate in a module with excellent cooling. (Semikron)

Many gate drivers are available today for power MOSFETs but they are not sufficient to drive GaN power devices. Special characteristics of GaN devices like fast switching characteristics and resulting high dV/dt, low threshold voltages for enhancement mode GaN devices and reduced maximum rating for the gate driving level require dedicated GaN drivers and an adapted module design. Also the intended increase in switching frequency requires optimized gate drivers and additional measures in board design to further decrease parasitic capacitance and inductance.

Fig. 1 shows an example for the state of the art system integration with Si-devices today. In the project the Si power devices (diodes, switches) should be replaced by

corresponding GaN-HEMT devices in a cascode topology with low voltage MOSFET in series and a freewheeling-diode in parallel and the whole assembly and the gate driver have to be adapted or developed to the needs of GaN devices.

### (b) Advances beyond the state of the art

In comparison to Si devices, GaN devices impose new possibilities and boundaries, which need to be explored. They enable the operation at high temperature conditions and higher switching speeds. Thus packaging is becoming the limiting factor. Classical solders do not withstand high operating temperatures and new approaches need to be evaluated in their feasibility (i.e. silver sintering, transient liquid phase bonding, etc.). Additionally the classical challenge of different CTE's will be even more severe. Thus the project is focused on the application of new interconnect technologies and new designs for reduced size and thermomechanical stresses. These approaches need to be designed, realised, evaluated and tested in order to achieve sufficient performance and lifetimes.

New concepts will be evaluated, because GaN devices are planar, which means that there is no current flow from top to bottom like in vertical Si devices. Therefore electrical contact is done from only one side of the chip. This enables alternative packaging constructions (i.e. Flip-Chip), which can give benefits to the thermal and electrical behaviour of the packaged device.

GaN enables operation at higher temperature and higher switching frequencies which demand for alternative module construction with assembly of the driver chips directly inside the module. This provides minimal parasitic inductance and capacitance between the driver and the GaN power transistors. This requires high temperature capable gate driver circuitry in order to benefit from the extended temperature capability of GaN power devices. In addition these high temperature capable modules also enable applications with high ambient temperatures up to 250 °C, like they are required for example in aeronautics, which is not accessible with standard CMOS bulk technologies. Final objective is to perform a complete validation of the power electronic system in terms of the inverter topology, isolation, driver and monitoring circuitry, sensors, cooling and high T/harsh environment reliability. System design and packaging issues will also be addressed and benchmarking with respect to Si and SiC will be performed.

Therefore this work will focus on a complete system innovation, which brings together the following tasks and expertises:

- Electrical system design including high temperature (250 ℃) gate drivers

- Package design supported by modelling (thermal, thermo-mechanical)

- Packaging technology and module assembly: "standard assembly" (soldering or gluing + thick wire bonding, flip chip technology) and new low temperature sinter assembly technology of GaN devices for higher operation temperatures and higher reliability etc.

- Advanced reliability testing

- Application circuit development for GaN devices

- Development of gate driver and monitoring circuits and their integration with high voltage isolation and for high temperature operation respectively

- Module demonstrators using conventional and novel topologies for different power system applications, e.g. inverters for industrial drives, power supplies, automotive and photo voltaic.

- System integration of GaN power devices, insulation and cooling, driver and sensor functions.

# 5.3 Selected end-user applications using GaN power devices

### (a) State of the art

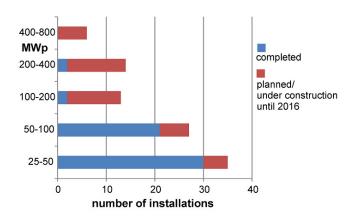

In this project the focus will be on two end application domains where GaN-based power devices are predicted to change to product landscape in the near future: photovoltaic and automotive. Both areas are interesting for their high volume market perspectives as well as for their specific technological challenges that might be overcome by making best use of the key features of GaN power devices.

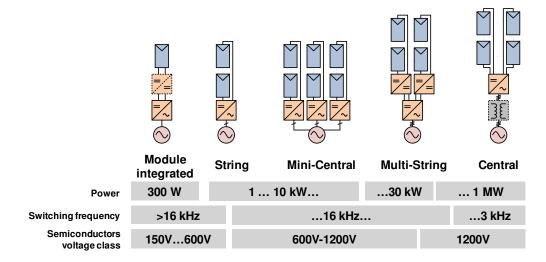

Figure 4: Grid connected PV system approaches and their corresponding frequency and power ranges.

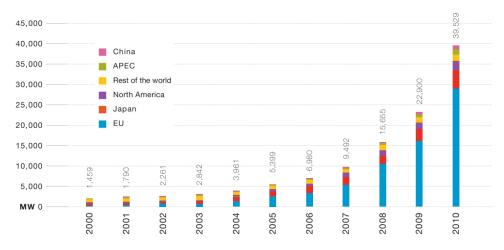

In Photovoltaic (PV), we observe a multitude of possible approaches concerning the array arrangement and the power conversion circuit properties as illustrated in Figure 4. This offers a diversified market where the introduction of new technologies can be performed in gradual steps going from lower to higher power levels, as chips with higher current ratings become available. As today, the most commonly used semiconductor technologies in PV power conversion are Si-IGBTs, Superjunction MOSFETs (up to 600V) and - in new designs - to a certain extent SiC-diodes.

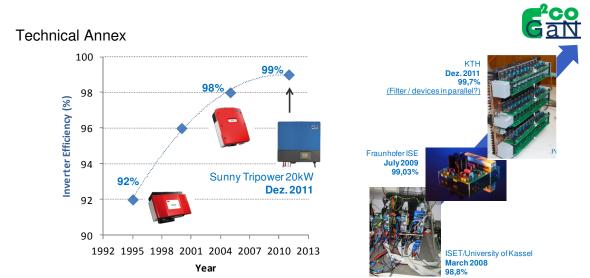

One of the key driving elements in the development of PV converters is the steady quest for higher efficiency levels (cf. Figure 5). These can in return be directly translated in lower installation costs (as fewer modules are required to produce the same energy) and faster payback time. Figure 5 shows an overview of the evolution of the efficiency levels of commercial products and R&D prototypes over the last ten years. Using SiC, spectacular levels of efficiency (99%) have already been achieved, but in many cases at prohibitive cost (e.g. by over sizing the active devices).

Figure 5: Grid efficiency development of commercial products and in R&D.

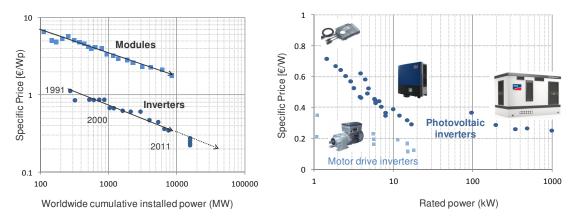

The real challenge is therefore to achieve very high levels of efficiency at an affordable, Si-comparable price – or better - below. Indeed, in the past there has been a pronounced trend towards continuous cost reduction of solar power inverters and modules. But still today, one can observe a significant price discrepancy between PV and motor drive inverters, especially at lower power ratings, demonstrating the remaining potential for cost reduction (cf. Figure 6). Another important challenge is the increase of reliability and elimination of failure modes of the power electronics system assuring low maintenance costs and stable and reliable grid supply.

Figure 6: PV inverter and module "learning curves" and comparison of the specific price as a function of power rating for PV and motor drive inverters.

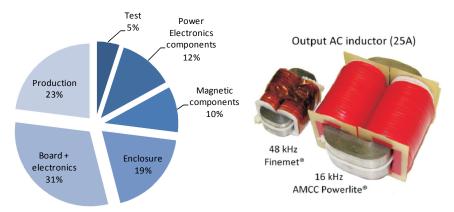

Figure 7 shows the cost break down of a PV inverter system. Only 12% of the system cost is directly linked to the power electronic components themselves. However, a smart choice of the power electronic components can have a significant impact on the expenditure on magnetic components and finally also the enclosure of the system, both elements being responsible of as much as 30% of the system cost as today. As illustrated in Figure 7, an increase of the switching frequency by a factor 4 enables a reduction in size (and cost) by approximately the same factor of the magnetic components.

Figure 7: Cost breakdown of PV inverters and possible size savings in filter inductors due to higher switching frequencies.

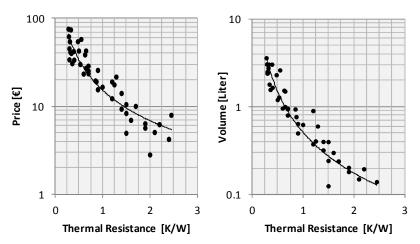

Also the cooling requirements play a very important role in the overall cost structure. When using high efficiency devices having very low heat dissipation and/or devices capable to operate at higher junction temperatures, designers can admit higher thermal resistances in the assembly, which gives access to immediate cost savings on system level as illustrated in Figure 8.

Figure 8: Price and volume of passive cooled heatsinks as a function of thermal resistance values.

<u>Automotive</u> applications, more specifically the multitude of power conversion systems used in novel hybrid and full electric vehicles, represent the second field of applications considered in this project to validate the GaN power device technology. As illustrated in Figure 9, the main characteristics and design targets are the extreme high levels of power density given size and weight constraints in transportable systems.

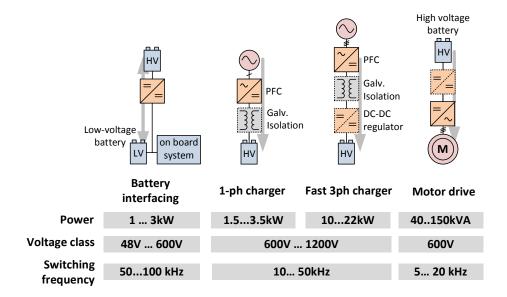

An overview of common conversion system concepts used in hybrid and full electric automotive applications together with the corresponding specifications is presented in Figure 10. Also in automotive, Si-IGBTs and Si-Diodes are the workhorses for most of the power conversion applications. Superjunction-MOSFETs are mainly applied at lower power levels (below 4kW). SiC diodes start to appear in some applications: used as freewheeling diodes parallel to Si IGBTs they can be used to improve the overall efficiency of conventional Si-based inverters to a certain extent.

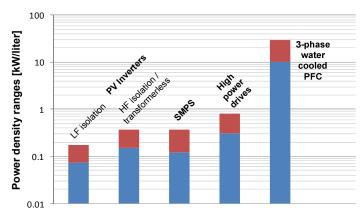

Figure 9: Comparison of power density levels for different power conversion applications

Figure 10: Overview of automotive main power conversion systems

These different conversion systems require different optimization approaches. Regarding the drive train, a high power density is less critical given the absence of output filters. As a consequence, the switching frequency is kept within a minimum level (linked to the engine rotation) in order to minimize losses in both semiconductor devices and the electric motor. Here, the reduction of losses in and the size of the power devices rather than high frequency capability will be the right criteria of choice of a new power device technology. Also operation at higher values of junction temperature (beyond 175°C) will be an asset: it lowers the cooling requirements and prevents from over sizing the converter, sometimes applied to deal with the limited temperature range. Within the E²COGaN project, the automotive inverter will be deemphasized as a demonstrator target as we do not regard as the most likely GaN power device target application.

So far, the more interesting applications are charging circuits for high voltage batteries with galvanic isolations. Here the combination of high frequency switching, low losses and high temperature capability is largely preferable to achieve an optimal design, featuring compactness, a simplified cooling system and high efficiency. The same properties would

also be beneficial for in DCDC power conversion for interfacing the high voltage battery pack to the 12V board net. Both applications therefore have been chosen as main demonstrator targets to validate the outcomes of GaN technologies at a system level.

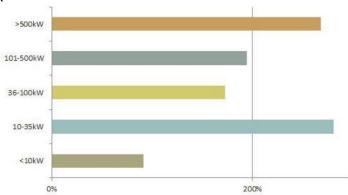

## (b) Advances beyond the state of the art

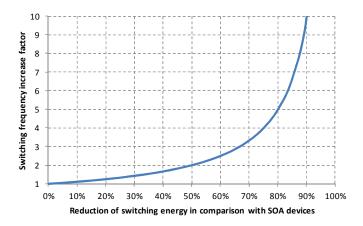

It has already been shown in literature that GaN power HEMTs have only 10% of the gate-drain capacitance for the same on-state resistance compared to Si power MOSFETs. As a consequence, the energy loss per switching event is by far lower than in a Si device. Similarly, GaN Schottky Barrier Diodes (SBDs) are by far more efficient than their Si counterparts due to the quasi-absence of reverse recovery charges. This reduction of the energy loss per switching event is – as stressed in Figure 11 - a key enabler for high frequency switching while not compromising the overall efficiency: to gain a factor of 10 in frequency, the energy loss has to be decreased by the same multiplier in order to enable and maintain the same efficiency level in the final application.

Nevertheless, a series of developments is still needed in order to reach the intrinsic potential of GaN power devices on system level. Very critical is an intelligent design of the package and/or module with low inductive commutation path (to limit the overvoltage) and low coupling capacitance to the package (to limit common mode currents). Directly connected with such developments is the necessity for new PCB (printed circuit board) design techniques focusing not only on low parasitics, but also on low electro-magnetic-emissions. As such tasks become increasingly difficult when moving in the direction of higher current ratings (due to paralleling), the option investigated inside the project, will be the external parallel connection by magnetic means which is expected to offer additional voltage levels in comparison with with natural interleaving technique.

Figure 11: Reduction of switching energy against SOA power device and achievable switching frequency factor considering same overall level of losses.

Concerning the PV system, we propose in a first step to increase the operation frequency from currently 16 to about 48 kHz under the assumption that the overall switching losses remain the same. The driving circuitry will need to be adapted to this high switching speed in order to guarantee reliable operation. Last but not least, the use of new materials for isolation interfaces in the board, inductors and capacitors will be investigated aiming to prevent possible damage from voltage transients and to ensure the required levels of lifetime. The GaN-on-Si devices as proposed within the scope of this project offer the unique combination of high efficiency, high frequency capability and attractive cost-perspective which is able to address the above cited development challenges in PV systems. Capable of

higher switching frequencies, GaN devices will open the way to a significant reduction in size of the magnetic components and finally in massive cost savings not only of the magnetic component itself but also on the enclosure making 30% of the total bill of materials.

Higher switching frequencies are also an advantage for battery chargers and DCDC converters in electric vehicles resulting in more compact systems. Both automotive and PV systems will benefit from higher junction temperature operation (beyond actual levels of 175°C) and better heat spreading (beyond 200W/cm²), that will be also investigated within the scope of this project. This will enable higher device loading and chip area savings. Also the cooling requirements will decrease. This is interesting for PV applications, but much more for automotive applications where water cooling systems might be replaced by cheaper natural or forced air cooling in some cases.

# 5.4 Summary of the expected results